Intel Launches Xeon 6+ "Clearwater Forest" Xeon with 288 E-Cores on 18A Process

Source: Techpowerup.com

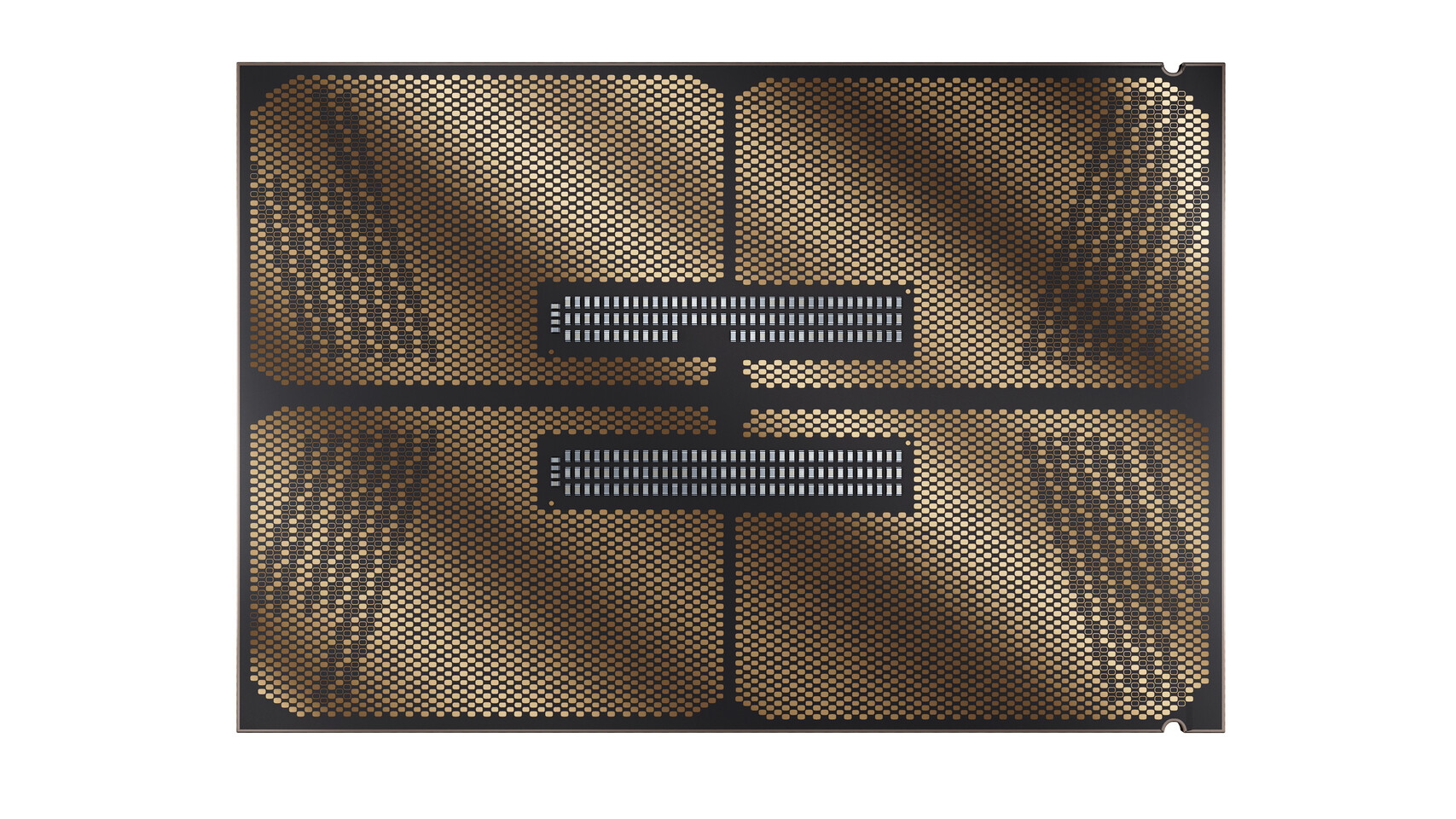

Intel used its MWC conference in Barcelona to showcase its most core-dense Xeon 6+ processor, codenamed "Clearwater Forest." As one of Intel’s most complex chiplet designs, the package combines twelve compute chiplets manufactured on an Intel 18A node with three active base tiles on Intel 3 and two I/O tiles on Intel 7. In this configuration, each compute tile contains six modules of four Darkmont efficiency cores, providing 24 E-cores per tile and a maximum of 288 Darkmont E-cores on a single socket. A two-socket system, therefore, approaches 576 cores. The design connects clusters with a high-bandwidth on-chip fabric and stacks die using Foveros Direct 3D, while EMIB links connect multiple tiles in a 2.5D arrangement.

Each Darkmont E-core comes with a 64 KB instruction cache, a wider front end, and a larger out-of-order window to sustain more in-flight work. Execution resources and the number of execution ports have been increased to improve parallel integer and vector throughput. Physically, clusters are grouped in four-core units sharing about 4 MB of L2 cache per group, and the package-level last-level cache can exceed a gigabyte, with about 1,152 MB of combined last-level cache across the package. "Clearwater Forest" supports the existing Xeon server platform socket, 12 memory channels, and broad I/O, including 96 PCIe 5.0 lanes and 64 CXL 2.0 lanes. Memory speed targets push toward DDR5-8000.